|

ENCYKLOPEDIA RADIOELEKTRONIKI I INŻYNIERII ELEKTRYCZNEJ Magistrala sterująca I2C. Encyklopedia elektroniki radiowej i elektrotechniki

Encyklopedia radioelektroniki i elektrotechniki / Komputery I2C to dwuprzewodowy interfejs opracowany przez firmę Philips. Oryginalna specyfikacja interfejsu miała maksymalną szybkość transmisji 100 Kb/s. Jednak z biegiem czasu pojawiły się standardy dotyczące szybszych trybów działania I2C. Do jednej opony I2C, można podłączyć urządzenia o różnych szybkościach dostępu, ponieważ szybkość transmisji danych jest określana przez sygnał zegarowy. Protokół transmisji danych jest zaprojektowany w taki sposób, aby gwarantował niezawodny odbiór przesyłanych danych. Podczas przesyłania danych jedno urządzenie pełni funkcję „Master”, które inicjuje transmisję danych i generuje sygnały synchronizacji. Kolejne urządzenie „Slave” – rozpoczyna transmisję dopiero na polecenie „Mastera”. W mikrokontrolerach PIC16CXXX tryb „Slave” urządzenia jest zaimplementowany sprzętowo w module SSP. Tryb „Master” jest zaimplementowany programowo. Podstawowe pojęcia używane przy opisie pracy autobusu I2C: Nadajnik - urządzenie przesyłające dane w autobusie Odbiorca - urządzenie odbierające dane z magistrali "Gospodarz" - urządzenie inicjujące transmisję i generujące sygnał zegarowy "niewolnik" - urządzenie, do którego dostęp ma "Master" Multi „Mistrz” - tryb autobusowy I2C z więcej niż jednym „Masterem” Arbitraż - procedura zapewniająca, że tylko jeden „Master” steruje magistralą Synchronizacja - procedura synchronizacji sygnału zegara z dwóch lub więcej urządzeń Stopnie wyjściowe kondycjonerów zegara (SCL) i danych (SDA) muszą być wykonane w obwodach otwartego kolektora (dren), aby połączyć kilka wyjść i podłączone do dodatniego zasilania przez zewnętrzny rezystor, aby uzyskać poziom „1” na magistrali, gdy żadne z urządzeń nie generuje sygnału „0”. Maksymalne obciążenie pojemnościowe jest ograniczone do 400pF. Inicjalizacja i zakończenie transferu danych Gdy nie ma transmisji danych na magistrali, sygnały SCL i SDA są wysokie ze względu na zewnętrzny rezystor. Sygnały START i STOP są generowane przez „Master” w celu określenia odpowiednio początku i końca transmisji danych. Sygnał START jest generowany przez przejście z wysokiego do niskiego sygnału SDA, podczas gdy sygnał SCL jest wysoki. Sygnał STOP jest zdefiniowany jako przejście SDA od niskiego do wysokiego, gdy SCL jest wysoki. Tak więc podczas przesyłania danych sygnał SDA może się zmieniać tylko wtedy, gdy sygnał SCL jest niski.

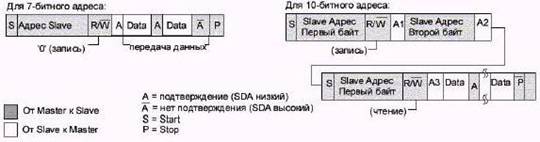

Adresowanie urządzeń na magistrali I2C Do adresowania urządzeń wykorzystywane są dwa formaty adresu: Prosty format 7-bitowy z bitem odczytu/zapisu R/W;

oraz format 10-bitowy - w pierwszym bajcie przesyłane są dwa najbardziej znaczące bity adresu i bit zapisu/odczytu, w drugim bajcie przesyłana jest dolna część adresu.

Potwierdzenie przyjęcia Podczas przesyłania danych, po każdym przesłanym bajcie, odbiorca musi potwierdzić odbiór bajtu sygnałem ACK. Jeżeli „Slave” nie potwierdzi odebrania adresu lub bajtu danych, „Master” musi przerwać transmisję wysyłając sygnał STOP. Podczas przesyłania danych z „Slave” do „Master”, „Master” generuje sygnały potwierdzenia odbioru danych ACK. Jeśli „Master” nie potwierdzi odebrania bajtu, „Slave” przestaje przesyłać dane, „zwalniając” linię SDA. „Master” może wtedy wygenerować sygnał STOP. Dla opóźnienia transmisji danych „Slave” może ustawić logiczne zero, wskazując „Masterowi” czekać. Po „uwolnieniu” linii SCL transmisja danych jest kontynuowana.

Transfer danych z „Master” do „Slave”

Odczytywanie danych z „Slave”

Korzystanie z sygnału ponownego START w celu uzyskania dostępu do „Slave”

Tryb multi-master Protokół komunikacyjny I2C pozwala mieć więcej niż jednego „Mastera” w magistrali. Funkcje arbitrażu i synchronizacji służą do rozwiązywania konfliktów na magistrali podczas inicjalizacji transferu. Arbitraż Arbitraż jest wykonywany na linii SDA, gdy linia SCL jest w stanie wysokim. Urządzenie, które podnosi linię SDA w stan wysoki, gdy inne wysyła stan niski, traci prawo do przejęcia „Master” i musi przejść w tryb „Slave”. „Master”, który utracił inicjatywę na magistrali, może generować impulsy zegarowe do końca bajtu, w którym utracił swoje właściwości „master”.

Synchronizacja Zegar na magistrali następuje po przeprowadzeniu arbitrażu na sygnale SCL. Gdy sygnał SCL przechodzi od wysokiego do niskiego, wszystkie zainteresowane urządzenia zaczynają odliczać czas trwania niskiego poziomu. Następnie urządzenia zaczynają zmieniać SCL z niskiego na wysoki zgodnie z wymaganą szybkością transmisji danych. Po przejściu poziomu od niskiego do wysokiego zainteresowane urządzenia liczą czas trwania wysokiego poziomu. Pierwsze urządzenie, które obniży sygnał SCL, określa parametry zegara.

Publikacja: cxem.net

Maszyna do przerzedzania kwiatów w ogrodach

02.05.2024 Zaawansowany mikroskop na podczerwień

02.05.2024 Pułapka powietrzna na owady

01.05.2024

▪ Nowe programowalne wielokanałowe 16-/14-bitowe przetworniki ADC ▪ Ładowarki do samochodów elektrycznych na parkingach ▪ Internet szerokopasmowy to niezbywalne prawo człowieka ▪ Przekształcanie wodoru w metal

▪ sekcja serwisu Parametry komponentów radiowych. Wybór artykułów ▪ artykuł Jamesa Brancha Cabella. Słynne aforyzmy ▪ artykuł Działka. Wskazówki podróżnicze ▪ artykuł Latający szalik. Sekret ostrości

Strona główna | biblioteka | Artykuły | Mapa stony | Recenzje witryn www.diagram.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

Zostaw swój komentarz do tego artykułu:

Zostaw swój komentarz do tego artykułu: